# Heterogate junctionless tunnel field-effect transistor: future of low-power devices

Shiromani Balmukund Rahi $^1$  · Pranav Asthana $^1$  · Shoubhik Gupta $^2$

© Springer Science+Business Media New York 2016

Abstract Gate dielectric materials play a key role in device development and study for various applications. We illustrate herein the impact of hetero (high-k/low-k) gate dielectric materials on the ON-current ( $I_{ON}$ ) and OFF-current ( $I_{OFF}$ ) of the heterogate junctionless tunnel field-effect transistor (FET). The heterogate concept enables a wide range of gate materials for device study. This concept is derived from the well-known continuity of the displacement vector at the interface between low- and high-k gate dielectric materials. Application of high-k gate dielectric material improves the internal electric field in the device, resulting in lower tunneling width with high  $I_{ON}$  and low  $I_{OFF}$  current. The impact of work function variations and doping on device performance is also comprehensively investigated.

**Keywords** Heterogate  $\cdot$  JLTFET  $\cdot$  Displacement vector  $\cdot$  High- $k \cdot$  Low- $k \cdot$  Tunneling width  $\cdot$  MOSFET  $\cdot$  Gate work function

## **1** Introduction

Aggressive scaling of bulk metal-oxide-semiconductor (MOS) FETs has played a significant role in the continu-

```

Shiromani Balmukund Rahi

sbrahi@iitk.ac.in

Pranav Asthana

pranavasthan32@gmail.com

Shoubhik Gupta

sgupta@fbk.eu

Department of Electrical Engineerin

```

<sup>1</sup> Department of Electrical Engineering, Indian Institute of Technology Kanpur, Kanpur 208016, India

<sup>2</sup> Electronics and Nano-scale Engineering Division, University of Glasgow, Glasgow, UK ous development of ultrascaled highly dense complementary MOS (CMOS) circuits for more than three decades. As conventional bulk MOSFETs are scaled down below 45 nm, short-channel effects (SCEs) and subthreshold leakage currents become more problematic [1]. The OFF-state leakage current ( $I_{OFF}$ ) is mainly responsible for the subthreshold power dissipation ( $I_{OFF} \cdot V_{DD}$ ) in very large-scale integration (VLSI) circuits. Due to their nonscalable subthreshold slope (SS) behavior at 300 K, MOSFETs fail to fulfill present requirements for low-power applications. Nowadays, a promising candidate to replace the conventional FET structure is the tunnel FET (TFET), which has become very attractive for use in ultralow-power applications due to its low OFF-current ( $I_{OFF}$ ) and stepper subthreshold slope (SS)

However, the tunneling FET structure suffers from lower ON-current than conventional MOSFETs due to tunneling current transport phenomena. To overcome this challenge of low ON-current ( $I_{ON}$ ), various approaches have been used to improve the electric field inside the tunneling region and reducing the effective tunneling bandgap [7–13]. However, lowering the bandgap increases  $I_{OFF}$  and limits the power supply scaling  $V_{DD}$  according to  $E_G \ge q V_{DD}$  [14–17].

At lower technology nodes, the requirement for shallow junctions is fulfilled by using the junctionless architecture proposed by Colinge [18–21], which is the focus of this work. Junctionless devices having no p-n junctions show improved device performance compared with conventional architectures based on p-n junctions. In this study, the advantages of the junctionless transistor are captured by adopting the junctionless TFET (JLTFET) structure. To improve the ON-current ( $I_{ON}$ ) and suppress the OFF-current ( $I_{OFF}$ ) as well as the subthreshold slope (SS), a brokenbandgap source/channel AlGaAs/Si semiconductor is used [18–26]. The remainder of this paper is arranged as follows:

Sect. 2 describes the simulation setup and device operation. Results and discussion are summarized in Sect. 3. Finally, concluding remarks are provided in Sect. 5.

#### 2 Simulation setup

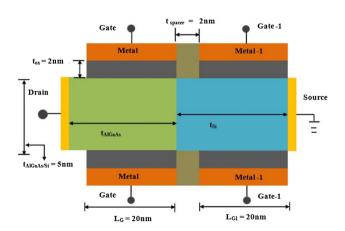

A schematic of the heterogate JLTFET considered in this work is shown in Fig. 1. The device structure is derived from a conventional p-i-n diode. The device has uniformly doped 5-nm-thick AlGaAs/Si with oxide thickness of 2 nm. Both the control gate length ( $L_{\rm G}$ ) and auxiliary gate length ( $L_{\rm G1}$ ) are 20 nm.

The transport phenomena in tunneling devices are completely different from those occurring in bulk MOSFET devices. Current conduction in the TFET is governed by band-to-band (B2B) tunneling from valence band of source to conduction band of channel [1–5]. Such B2B tunneling is much more sensitive to material/device parameters such as energy bandgap ( $E_G$ ), dielectric thickness ( $t_{ox}$ ), dielectric constant of the gate material (k), and effective mass of charge carriers ( $m^*$ ), according to Eq. 1 [1,5,7,10]:

$$T(E) = \exp\left(-\frac{4\sqrt{2m^*}E_{\rm G}^{3/2}}{3|e|\hbar(\Delta\Phi + E_{\rm G})}\lambda\right),\tag{1}$$

where  $\lambda$  is the tunneling distance between source and channel, given by

$$\lambda = \sqrt{(\varepsilon_{\rm Si}/\varepsilon_{\rm ox})} t_{\rm ox} t_{\rm Si}.$$

In Eq. 1,  $m^*$  is the effective mass,  $\Delta \Phi$  is the band energy difference between conduction band of source and valence band of channel,  $\hbar$  and q are the reduced Planck constant and electron charge, respectively, while  $t_{ox}$  and  $t_{Si}$  are the phys-

Fig. 1 Device structure and parameters of the heterogate junctionless TFET

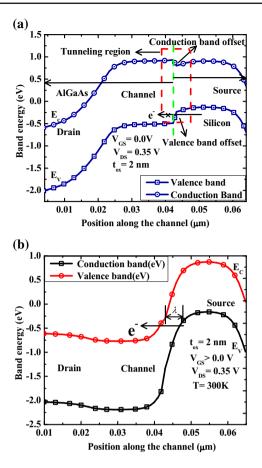

**Fig. 2** Simulated band structure of the heterogate JLTFET: **a** OFFstate ( $V_{\text{GS}} = 0.0$  V) and **b** ON-state ( $V_{\text{GS}} = 1.0$  V) at  $V_{\text{DS}} = 0.35$  V for high-k gate material HfO<sub>2</sub> (k = 25)

ical oxide thickness and semiconductor channel thickness, respectively.

In this work, simulations were carried out using Silvaco Atlas [23,25,26]. In the simulations, a nonlocal model was considered for band-to-band tunneling of charge carriers between source and channel. Due to the high doping level, a source bandgap narrowing (BGN) model was also included, because the effective bandgap directly influences the tunneling current. We included a Shockley–Read–Hall (SRH) recombination model due to the presence of high impurity atom concentration in the channel and Fermi–Dirac statistics to calculate the intrinsic carrier concentration. For more accurate current calculations, Schenk's trap-assisted tunneling (TAT), drift–diffusion current transport model, and quantum confinement (QC) models were also included [23,27,28].

The simulated energy-band diagram for OFF-state ( $V_{GS} = 0.0 \text{ V}$ ) and ON-state ( $V_{GS} = 1.0 \text{ V}$ ) are shown in Fig. 2. Figure 2a shows the OFF-state behavior of the device, revealing that the tunneling width ( $\lambda$ ) is larger as a result of the small leakage current. In the ON-state condition (Fig. 2b), the tunneling width ( $\lambda$ ) reduces as a result of the increased tunneling

probability of charge carriers from valence band of source to conduction band of channel.

## 3 Results and discussion

Tunnel FETs suffer from low ON-current ( $I_{ON}$ ) due to the B2B tunneling mechanism. The tunneling current largely depends on the tunneling distance ( $\lambda$ ). Minor changes in device parameters such as the bandgap ( $E_g$ ), oxide gate material, etc. can improve the ON-current ( $I_{ON}$ ) [29–31], as discussed in Sect. 2, and the TFET characteristics are even more sensitive to the oxide thickness ( $t_{ox}$ ), doping profile, and dielectric constant of the gate material (k). In this section, the effect of high-k dielectric, gate work function, and source/channel/drain doping profile on device characteristics is presented based on simulation results and discussed in detail.

#### 3.1 Impact of high-k gate materials

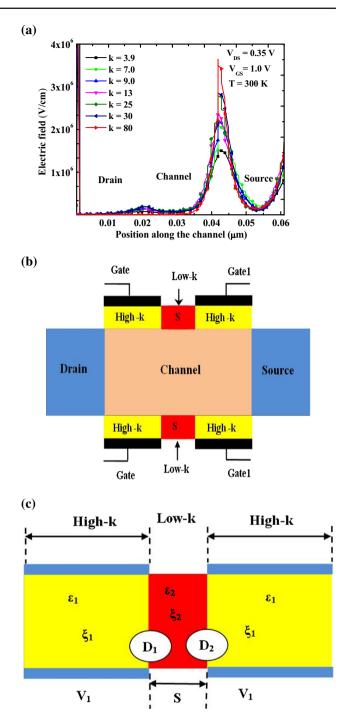

Figure 3a compares the electric field profile inside a heterogate JLTFET. Conventionally, the electric field in this device is given by Eq. (2), where S is the separation between the high-k and low-k material.

$$\xi \approx \frac{V_1 - V_2}{S}.\tag{2}$$

As shown in Fig. 3b, c, when using a high-*k* dielectric in the heterogate JLTFET, at the interface between the dielectrics, the displacement vector  $(D = \varepsilon \xi)$  should be continuous [8]:

$$\varepsilon_1 \xi_1 = \varepsilon_2 \xi_2, \tag{3}$$

$$\xi_2 = \left(\frac{\varepsilon_1}{\varepsilon_2}\right)\xi_1. \tag{4}$$

At the interface between the high-k and low-k dielectric, one has

$$\varepsilon_1 \gg \varepsilon_2$$

(5)

$$\xi_2 > \xi_1; \tag{6}$$

i.e. the electric field is larger toward the low-*k* dielectric, strongly supporting the asymmetric electric field behavior of TFET devices as shown in Fig. 3a. The physical interpretation of the displacement vector in a heterogate JLTFET is shown in Fig. 3b. Application of a high-*k* gate material in a heterogate JLTFET increases the electric field lines from the source side and reduces the barrier width near the source–channel interface. The electric field variation along the channel in a heterogate JLTFET with different gate dielectric materials

Fig. 3 a Electric field distribution along the channel for various gate dielectric materials in the ON-state. **b** Physical interpretation of displacement vector in the heterogate JLTFET. **c** Illustration of the electric field amplification using low-k/high-k dielectrics in the heterogate JLTFET

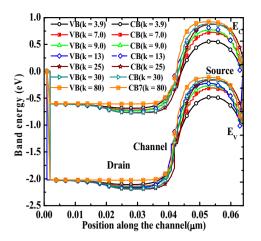

is shown in Fig. 3a. As the k value of the gate material is varied from low to high, the electric field increases and the peak electric field shifts towards the source end. Due to this increased electric field, the conduction as well as valence

Fig. 4 Band shift versus gate dielectric material in the ON-state

**Fig. 5** a Tunneling barrier width  $(\lambda)$  modulation versus various gate dielectric materials for  $t_{ox} = 2 \text{ nm}$ ,  $N_d = 1 \times 10^{19}/\text{cm}^3$ , and spacer = 2 nm for SiO<sub>2</sub> (k = 3.9). **b** Measurement procedure for tunneling barrier width ( $\lambda$ ) of **a**, using the WKB triangular potential approximation

band move upwards, as shown in Fig. 4. This upward shift of the bands reduces the tunneling barrier ( $\lambda$ ).

As per Eq. 1, the quantum-mechanical tunneling probability is an exponential function of barrier width ( $\lambda$ ). Figure 5a shows the variation of the energy barrier width ( $\lambda$ ) reduction versus the gate dielectric material for the simulated device.

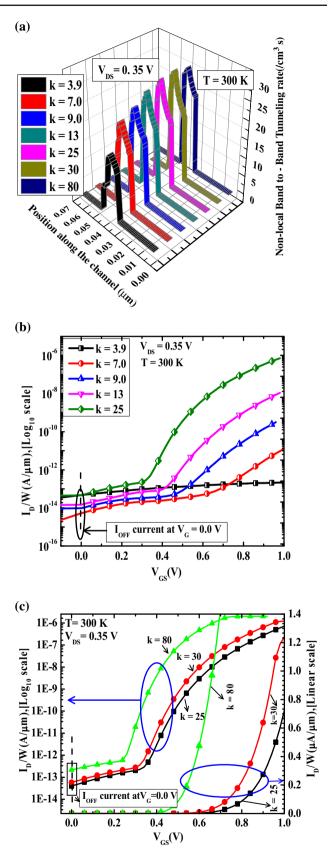

Fig. 6 Impact of high-*k* gate dielectric on **a** nonlocal band-to-band (B2B) tunneling rate, **b** and **c**  $I_{\rm D}-V_{\rm G}$  characteristics for drain voltage  $V_{\rm DS} = 0.35 \,\rm V$

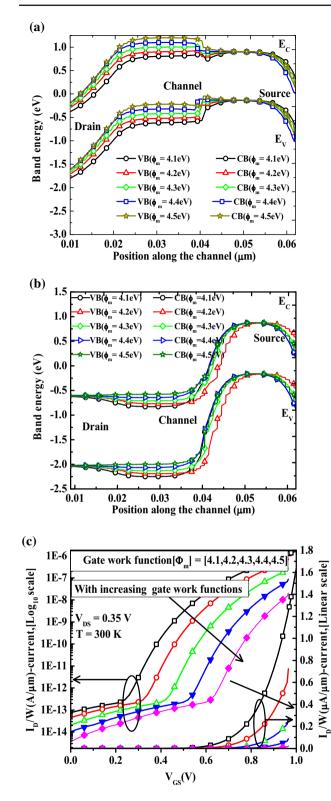

Fig. 7 Effect of control gate work function on the band diagram in **a** the OFF-state and **b** the ON-state, and **c** the  $I_D-V_G$  characteristic

The simulation results strongly support the variation behavior of the tunneling distance with the gate dielectric material [9]. Figure 5b shows a graphical representation of the technique used for measurement of the tunneling barrier width

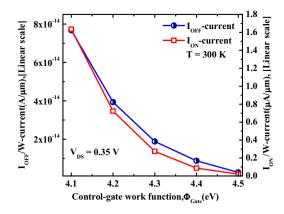

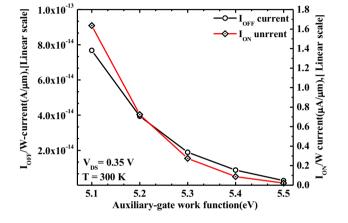

Fig. 8  $I_{\rm ON}$ ,  $I_{\rm OFF}$  current variation for the considered device when varying the control gate work function with  $N_{\rm d} = 1 \times 10^{19}/{\rm cm}^3$ ,  $t_{\rm ox} = 2$  nm, spacer = 5 nm, and  $\Phi_{\rm m1} = 5.2 \,{\rm eV}$

( $\lambda$ ), adopting the Wentzel–Kramers–Brillouin (WKB) triangular potential approximation [11].

The reduction of the tunneling barrier width  $(\lambda)$  when employing a high-k gate dielectric material results in high electric field that improves the Zener tunneling rate of electrons from valence band  $(E_V)$  of source to conduction band of channel. The simulated nonlocal B2B tunneling rate versus the high-k gate material for the heterogate JLTFET device is shown in Fig. 6, revealing improved nonlocal tunneling in the device. The tunneling rate extracted for the simulated device varies from 5.0 to 27.5/cm<sup>3</sup> s for the various gate dielectric materials with k = 3.9 - 80, as shown in Fig. 6a. The ON-current  $(I_{ON})$  is proportional to the electron tunneling rate, which according to Eq. 1 is dependent on the tunneling barrier width ( $\lambda$ ). Therefore, the reduction in the tunneling barrier width ( $\lambda$ ) when using a high-k dielectric gate material will increase the drain current as compared with low-k dielectric material.

In TFETs, the ON-current  $(I_{ON})$  is proportional to the electron tunneling rate, which follows the transmission probability  $T_{\text{WKB}}$  according to Eq. (1). The effect of high-k gate material on the  $I_{\rm D}-V_{\rm G}$  characteristic of the heterogate JLTFET device is shown in Fig. 6b, c. The high-k gate material increases the capacitive coupling, resulting in a major improvement in  $I_{ON}$  as well as the average subthreshold swing (SS) [8]. Based on the WKB tunneling probability in Eq. (1), the tunneling current increases when increasing the electric field along the channel, as shown in Fig. 3a. One way of increasing the electric field is by decreasing the oxide thickness  $(t_{ox})$ . However, a critical decrease in oxide thickness also increases the gate leakage current, so a tradeoff between  $I_{ON}$  and  $I_{OFF}$  applies when varying  $t_{ox}$ , and one cannot use this approach to improve  $I_{ON}$  at the cost of  $I_{OFF}$ . The impact of high-k gate materials on the  $I_D-V_G$  characteristic of the heterogate JLTFET is shown in Fig. 6b, c, revealing a significant improvement in  $I_{ON}$  due to the reduction of  $\lambda$  with

high-*k* gate materials, as shown in Fig. 5a. One can observed from Fig. 6 that, by adopting a suitable high-*k* gate material,  $I_{ON}$ ,  $I_{OFF}$ , and the subthreshold slope (calculated by Eq. 2) can be improved [5]. The average subthreshold slope for high-*k* gate materials HfO<sub>2</sub> (k = 25), La<sub>2</sub>O<sub>3</sub> (k = 30), and TiO<sub>2</sub> (k = 80) was 48.2, 47.2, and 43.9 mV/dec, respectively. However, Si<sub>3</sub>N<sub>4</sub> (k = 7.0), Al<sub>2</sub>O<sub>3</sub> (k = 9.0), and Y<sub>2</sub>O<sub>3</sub> (k = 13) showed average subthreshold slope (SS) of 103.4, 75.6, and 59.0 mV/dec, respectively.

The  $I_{\rm ON}$  value for the simulated device was  $7.2 \times 10^{-7}$ ,  $1.2 \times 10^{-6}$ , and  $2.0 \times 10^{-6}$  A/µm for high-k gate dielectric materials HfO<sub>2</sub> (k = 25), La<sub>2</sub>O<sub>3</sub> (k = 30), and TiO<sub>2</sub> (k = 80), respectively. The leakage current at  $V_{\rm GS} = 0.0$  V varied from  $\sim 10^{-15}$  to  $\sim 10^{-14}$  A/µm for Si<sub>3</sub>N<sub>4</sub> (k = 7.0), Al<sub>2</sub>O<sub>3</sub> (k = 9.0), Y<sub>2</sub>O<sub>3</sub> (k = 13), HfO<sub>2</sub> (k = 25), La<sub>2</sub>O<sub>3</sub> (k = 30), and TiO<sub>2</sub> (k = 80) [27,28]. However,  $I_{\rm OFF}$  for TiO<sub>2</sub> was  $\approx 10^{-14}$  to  $10^{-13}$  A/µm. Investigation of the device with high-k dielectric materials such as HfO<sub>2</sub> (k = 25), La<sub>2</sub>O<sub>3</sub> (k = 30), and TiO<sub>2</sub> (k = 80) revealed  $I_{\rm ON}/I_{\rm OFF}$  ratios of  $\approx 10^8$  for optimized device parameter combinations. The gate work functions  $\Phi_{\rm m}$ ,  $\Phi_{\rm m1}$ , and the source/channel/drain doping were taken as 4.2 eV, 5.2 eV, and  $1 \times 10^{19}$ /cm<sup>3</sup>, respectively.

$$SS = V_{DD} / \log_{10} \left( I_{ON} / I_{OFF} \right).$$

<sup>(7)</sup>

## 3.2 Impact of gate work function

Figure 7a, b shows the change in the energy-band diagram for the device when varying  $\Phi_m$  to 4.1, 4.2, 4.3, 4.4, and 4.5 eV for  $\Phi_{m1}$  of 5.2 eV. The effect of  $\Phi_m$  on  $I_D-V_G$  is shown in Fig. 7c. A lower gate work function ( $\Phi_m$ ) results in more band bending in the channel near the source–channel junction [29–31], which helps to improve the  $I_{ON}$  characteristics of the device, as shown in Fig. 7.

This also increases  $I_{OFF}$ , as shown in Fig. 8. In OFF-state, lower  $\Phi_{\rm m}$  values (4.1 eV  $\leq \Phi_{\rm m} \leq 4.5$  eV) move the band downward in the channel region, as shown in Fig. 7a. This leads to an increase in the OFF-state  $I_{OFF}$  value of the simulated device, as shown in Fig. 8. The simulated ON-state band diagram in Fig. 7b shows a larger  $\Phi_{\rm m}$  value, bending the band along the channel. This occurs due to coupling between the gate and channel. This reduces the tunneling probability and increases the threshold voltage ( $V_{\rm TH}$ ), leading to the reduction of  $I_{\rm ON}$  seen in Fig. 8.

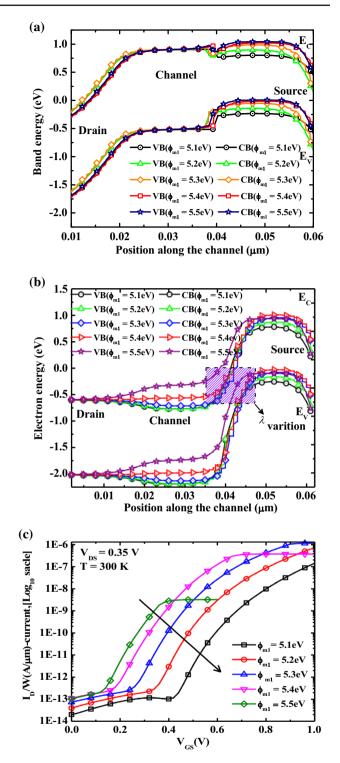

Furthermore, the impact of the auxiliary gate work function ( $\Phi_{m1}$ ) of the heterogate JLTFET was investigated in detail. To do this, the auxiliary gate  $\Phi_{m1}$  was varied to 5.1, 5.2, 5.3, 5.4, and 5.5 eV while keeping  $\Phi_m$  constant at 4.2 eV. The OFF-state and ON-state and the  $I_D-V_G$  characteristic of the simulated device are shown in Fig. 9. Figure 9a, b shows the change in the band diagram versus  $\Phi_{m1}$  while keeping  $\Phi_m$ at 4.2 eV. As  $\Phi_{m1}$  is increased, the tunneling width ( $\lambda$ ) also

Fig. 9 Effect of auxiliary gate work function ( $\phi_{m1}$ ) on the band diagram in **a** the OFF-state and **b** the ON-state, and **c** the  $I_D-V_G$  characteristic

increases, resulting in lower  $I_{ON}$  as well as  $I_{OFF}$ . This is due to the higher  $\Phi_{m1}$  value pushed upward along the channel, as shown in Fig. 9a.

Table 1 Average subthreshold slope of the simulated device in Fig. 1 with HfO<sub>2</sub> for  $V_{\rm DS} = 0.35$  V

| S. no. | Group 1                                         |                                                |                                     | Group 2                                         |                                                |                                     |

|--------|-------------------------------------------------|------------------------------------------------|-------------------------------------|-------------------------------------------------|------------------------------------------------|-------------------------------------|

|        | Control gate work function, $\Phi_{\rm m}$ (eV) | Auxiliary gate work function, $\Phi_{m1}$ (eV) | Average subthreshold slope (mV/dec) | Control gate work function, $\Phi_{\rm m}$ (eV) | Auxiliary gate work function, $\Phi_{m1}$ (eV) | Average subthreshold slope (mV/dec) |

| 1      | 4.1                                             | 5.2                                            | 48.7                                | 4.2                                             | 5.1                                            | 52.0                                |

| 2      | 4.2                                             | 5.2                                            | 48.2                                | 4.2                                             | 5.2                                            | 48.2                                |

| 3      | 4.3                                             | 5.2                                            | 49.5                                | 4.2                                             | 5.3                                            | 48.6                                |

| 4      | 4.4                                             | 5.2                                            | 50.8                                | 4.2                                             | 5.4                                            | 53.6                                |

| 5      | 4.5                                             | 5.2                                            | 52.0                                | 4.2                                             | 5.5                                            | 77.8                                |

**Fig. 10**  $I_{\rm ON}$ ,  $I_{\rm OFF}$  current variation for the considered device when varying the auxiliary gate work function ( $\Phi_{\rm m1}$ ) with  $N_{\rm d} = 1 \times 10^{19}$ /cm<sup>3</sup>,  $t_{\rm ox} = 2$  nm,  $t_{\rm spacer} = 5$  nm, and  $\Phi_{\rm m} = 4.2$  eV

Table 1 summarizes the average subthreshold slope values extracted for different  $\Phi_{\rm m}$  and  $\Phi_{\rm m1}$  values. For work functions of 4.2 and 5.2 eV, the considered device showed optimized performance. The variation of  $I_{\rm ON}$  and  $I_{\rm OFF}$  versus the auxiliary gate work function  $\Phi_{\rm m}$  is shown in Fig. 10.

## 4 Impact of doping

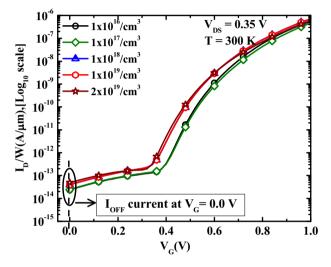

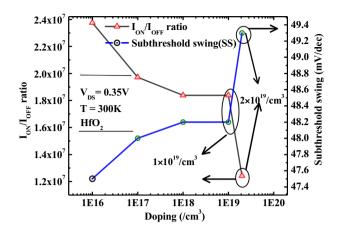

This section is dedicated to the impact of doping variation on the device. To see the influence of source/channel/drain doping in the heterogate JLTFET, we used various uniform doping profiles of source/channel/drain, such as  $1 \times 10^{16}$ ,  $1 \times 10^{17}$ ,  $1 \times 10^{18}$ ,  $1 \times 10^{19}$ , and  $2 \times 10^{19}$ /cm<sup>3</sup>. The  $I_{\rm D}$ - $V_{\rm G}$  characteristics of the heterogate JLTFET for the different doping levels are shown in Fig. 11. For the simulations shown in Fig. 11, we used  $\Phi_{\rm m}$ ,  $\Phi_{\rm m1}$ ,  $V_{\rm DS}$ , and  $V_{\rm G1}$  values of 4.2 eV,  $5.2 \,{\rm eV}$ ,  $0.35 \,{\rm V}$ , and  $0.0 \,{\rm V}$ , respectively. The  $I_{\rm ON}$  and  $I_{\rm OFF}$  currents for the simulated device for these different doping levels are presented in Table 2. The variation of  $I_{\rm ON}/I_{\rm OFF}$  and the average subthreshold slope for the investigated doping range is shown in Fig. 12. The considered device showed a small variation for doping of  $1 \times 10^{16}$ ,  $1 \times 10^{17}$ ,  $1 \times 10^{18}$ , and

Fig. 11 Effect of doping on the transfer characteristics of the considered device in source/channel/drain

Table 2 Electrical parameters extracted for the simulated device

| S. no. | Doping $(cm^{-3})$ | $I_{\rm OFF}~({\rm A}/\mu{\rm m})$ | $I_{\rm ON}~({\rm A}/\mu{\rm m})$ |

|--------|--------------------|------------------------------------|-----------------------------------|

| 1      | $1 \times 10^{16}$ | $2.3 \times 10^{-14}$              | $5.5 	imes 10^{-7}$               |

| 2      | $1 \times 10^{17}$ | $2.4 \times 10^{-14}$              | $4.7 \times 10^{-7}$              |

| 3      | $1 \times 10^{18}$ | $3.9 	imes 10^{-14}$               | $7.2 \times 10^{-7}$              |

| 4      | $1 \times 10^{19}$ | $3.9 \times 10^{-14}$              | $7.2 \times 10^{-7}$              |

| 5      | $2 \times 10^{19}$ | $4.8 \times 10^{-14}$              | $6.0 	imes 10^{-7}$               |

$1 \times 10^{19}$ /cm<sup>3</sup>. However, doping the adopted device with  $N_{\rm d} > 1 \times 10^{19}$ /cm<sup>3</sup> is not useful due to its limited  $I_{\rm ON}/I_{\rm ON}$  ratio. The subthreshold slope also starts to increase rapidly for  $N_{\rm d} > 1 \times 10^{19}$ /cm<sup>3</sup>, as shown in Fig. 10.

## **5** Conclusions

A detailed study of the heterogate JLTFET using the displacement vector concept is reported based on two-dimensional (2-D) simulations. The results demonstrate that the wide range of heterogate dielectric materials can enable mod-

Fig. 12 Influence of doping profile on the  $I_{ON}/I_{OFF}$  ratio and average subthreshold slope at  $V_{GS} = 1.0$  V and  $t_{ox} = 2$  nm

ulation of the device characteristics. The applied method provides high performance and high electric field in the heterogate JLTFET as a result of the combination of high-kand low-k dielectric materials. In summary, a new highperformance heterogate JLTFET is studied thoroughly, offering simulated results including  $I_{\rm ON} \approx 1.2 \times 10^{-6} \, {\rm A}/{\mu}{\rm m}$  and  $I_{\text{OFF}} \approx 10^{-14} \text{ A}/\mu \text{m}$  for La<sub>2</sub>O<sub>3</sub>.  $I_{\text{ON}}/I_{\text{OFF}} \approx 10^8$  and subthreshold slope of  $\approx 47.2 \,\text{mV/dec}$  were obtained for the same dielectric. The performance of the heterogate JLTFET is mainly governed by the internal electric field inside the channel. Use of heterogate dielectric materials results in improved electric field. Use of high-k gate material improves  $I_{ON}$ ,  $I_{OFF}$ , as well as the subthreshold slope of the device, while low-kgate material results in low  $I_{ON}$  and also degrades the subthreshold slope. It is also observed that, by changing the gate dielectric, the subthreshold slope can be modulated.

Work function engineering of gate materials also plays a significant role in modulating the threshold for charge tunneling from source to channel. Detailed study of the work function is also presented herein. Moreover, bandgap narrowing due to the high doping level in the device is also studied.

#### References

- Khatami, Y., Banerjee, K.: Steep subthreshold slope n- and p-type tunnel-FET devices for low-power and energy-efficient digital circuits. IEEE Trans. Electron Devices 56(11), 2752–2761 (2009)

- Kim, J.J., Roy, K.: Double gate-MOSFET subthreshold circuit for ultralow power applications. IEEE Trans. Electron Devices 51(9), 1468–1474 (2004)

- Lu, H., Seabaugh, A.: Tunnel field-effect transistors: state-of-theart. IEEE J. Electron Devices Soc. 2(4), 44–49 (2014)

- Huang, Q., Huang, R., Chen, S., Wu, J., Zhan, Z., Qiu, Y., Wang, Y.: Device physics and design of T-gate Schottky barrier tunnel FET with adaptive operation mechanism. Semicond. Sci. Technol. 29(9), 095013 (2014)

- Ionescu, A.M., Riel, H.: Tunnel field-effect transistors as energyefficient. Nature 479, 329–337 (2011)

- Knoch, J., Mantl, S., Appenzeller, J.: Impact of the dimensionality on the performance of tunneling FETs: bulk versus one-dimensional devices. Solid-State Electron. 51(4), 572–578 (2007)

- Ilatikhameneh, H., Ameen, T.A., Klimeck, G., Appenzeller, J., Rahman, R.: Dielectric engineered tunnel field-effect transistor. IEEE Electron Device Lett. 36(10), 1097–1100 (2015)

- Boucart, K., Ionescu, A.M.: A new definition of threshold voltage in tunnel FETs. Solid-State Electron. 52(9), 1318–1323 (2008)

- Boucart, K., Ionescu, A.M.: Double gate tunnel FET with ultrathin silicon body and high-k gate dielectric. IEEE Trans. Electron Devices 54(7), 1725–1733 (2007)

- Choi, W.Y., Park, B.G., Lee, J.D., Liu, T.J.K.: Tunneling fieldeffect transistors (TFETs) with subthreshold swing (SS) less than 60 mV/dec. IEEE Electron Device Lett. 28(8), 743–745 (2007)

- Jhaveri, R., Nagavarapu, V., Woo, J.C.: Effect of pocket doping and annealing schemes on the source-pocket tunnel field-effect transistor. IEEE Trans. Electron Devices 58(1), 80–86 (2011)

- Venkatagirish, N., Tura, A., Jhaveri, R., Chang, H. Y., Woo, J.: The tunnel source MOSFET: a novel asymmetric device solution for ultra-low power applications. In: 2009 IEEE International Conference on IC Design and Technology (pp. 155–159). IEEE, Piscataway (2009)

- Zhang, Q., Zhao, W., Seabaugh, A.: Low-subthreshold-swing tunnel transistors. IEEE Electron Device Lett. 27(4), 297–300 (2006)

- Kanungo, S., Rahaman, H., Gupta, P.S., Dasgupta, P.S.: A detail simulation study on extended source ultra-thin body double-gated tunnel FET. In: 2012 5th International Conference on Computers and Devices for Communication (CODEC, December) (pp. 1–4). IEEE, Piscataway (2012)

- Wang, X.D., Xiong, Y., Tang, M.H., Peng, L., Xiao, Y.G., Xu, X.Y., He, J.H.: A Si tunnel field-effect transistor model with a high switching current ratio and steep sub-threshold swing. Semicond. Sci. Technol. 29(9), 095016 (2014)

- Qiu, Y., Wang, R., Huang, Q., Huang, R.: A comparative study on the impacts of interface traps on tunneling FET and MOSFET. IEEE Trans. Electron Devices 61(5), 1284–1291 (2014)

- Lee, C.W., Afzalian, A., Akhavan, N.D., Yan, R., Ferain, I., Colinge, J.P.: Junctionless multigate field-effect transistor. Appl. Phys. Lett. 94(5), 053511 (2009)

- Lee, C.W., Ferain, I., Afzalian, A., Yan, R., Akhavan, N.D., Razavi, P., Colinge, J.P.: Performance estimation of junctionless multigate transistors. Solid-State Electron. 54(2), 97–103 (2010)

- Colinge, J.P., Kranti, A., Yan, R., Lee, C.W., Ferain, I., Yu, R., Razavi, P.: Junctionless nanowire transistor (JNT): properties and design guidelines. Solid-State Electron. 65, 33–37 (2011)

- Asthana, P.K., Ghosh, B., Rahi, S.B.M., Goswami, Y.: Optimal design for a high performance H-JLTFET using HfO<sub>2</sub> as a gate dielectric for ultra low power applications. RSC Adv. 4(43), 22803– 22807 (2014)

- Rahi, S.B., Ghosh, B., Asthana, P.: A simulation-based proposed high-k heterostructure AlGaAs/Si junctionless n-type tunnel FET. J. Semicond. 35(11), 114005 (2014)

- Rahi, S.B., Ghosh, B., Bishnoi, B.: Temperature effect on hetero structure junctionless tunnel FET. J. Semicond. 36(3), 034002 (2015)

- Rahi, S.B., Ghosh, B.: High-k double gate junctionless tunnel FET with a tunable bandgap. RSC Adv. 5(67), 54544–54550 (2015)

- Villani, F., Gnani, E., Gnudi, A., Reggiani, S., Baccarani, G.: A quasi 2D semianalytical model for the potential profile in hetero and homojunction tunnel FETs. Solid-State Electron. **113**, 86–91 (2015)

- Silvaco, Version 5.15.32.R. (2015). http://www.silvaco.com (2015, Jul.) Atlas User's Manual. http://www.silvaco.com

- Robertson, J.: High dielectric constant oxides. Eur. Phys. J. Appl. Phys. 28(3), 265–291 (2004)

- Holtij, T., Graef, M., Kloes, A., Iñíguez, B.: Modeling and performance study of nanoscale double gate junctionless and inversion mode MOSFETs including carrier quantization effects. Microelectron. J. 45(9), 1220–1225 (2014)

- Graef, M., Holtij, T., Hain, F., Kloes, A., Iñíguez, B.: A 2D closed form model for the electrostatics in hetero-junction double-gate tunnel-FETs for calculation of band-to-band tunneling current. Microelectron. J. 45(9), 1144–1153 (2014)

- Dutta, T., Kumar, S., Rastogi, P., Agarwal, A., Chauhan, Y.S.: Impact of channel thickness variation on bandstructure and sourceto-drain tunneling in ultra-thin body III-V MOSFETs. IEEE J. Electron Devices Soc. 4(2), 66–71 (2016)

- Yadav, C., Duarte, J.P., Khandelwal, S., Agarwal, A., Hu, C., Chauhan, Y.S.: Capacitance modeling in III-V FinFETs. IEEE Trans. Electron Devices 62(11), 3892–3897 (2015)

- Patel, N., Ramesha, A., Mahapatra, S.: Drive current boosting of ntype tunnel FET with strained SiGe layer at source. Microelectron. J. 39(12), 1671–1677 (2008)